### SHF Communication Technologies AG

Wilhelm-von-Siemens-Str. 23D • 12277 Berlin • Germany

Phone +49 30 772051-0 • Fax +49 30 7531078

E-Mail: sales@shf-communication.com • Web: www.shf-communication.com

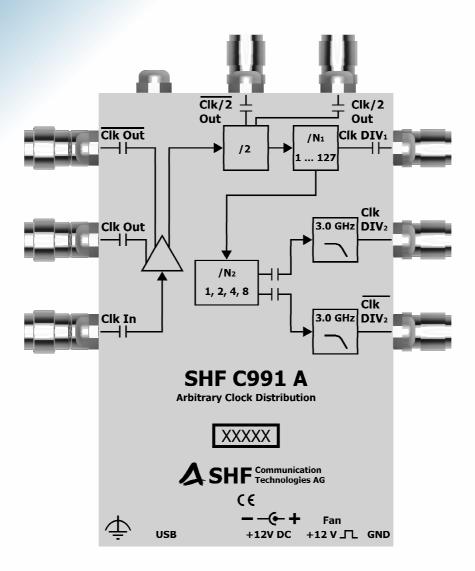

# Datasheet SHF C991 A Arbitrary Clock Distribution

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 1/18

# Description

The SHF C991 A is a versatile broad band clock distribution providing copies of the incoming clock at different divider ratios.

### Features

- Broadband operation from 4 to 64 GHz.

- Multiple clock outputs at different divider ratios.

- Controlled by intuitive graphical user interface BERT Control Center (BCC) via USB

- Controlled by intuitive graphical user interface SHF Control Center (SCC) via USB

### Applications

Test setups are always an interaction of different parts; sophisticated setups may include many different instruments and modules. To operate concurrently a common clock signal is often indispensable. However, frequency requirements of the instruments and modules are very different. A clock distribution is supposed to provide clock signals derived from the master clock (input) at a frequency fraction exactly fitting to the individual requirements.

Some examples for a high-speed (> 40 GHz) clock system are a listed below:

- The clock input is fed with a signal from a signal generator like the SHF 78122 A.

- The full clock outputs can be used to drive remote heads like SHF's DACs, Multiplexers, Demultiplexers or PAM-Multiplexers.

- By selecting the appropriate fraction of the Clock DIV<sub>1</sub> output almost all precision time bases, or phase references of commercially available equivalent-time sampling scopes can be driven.

- By setting the LPF Clock output to the appropriate frequency band, the derived signal can be used to synchronize the AWGs with external clock domains and with minimum possible timing jitter, avoiding additional phase-locked-loops which are sometimes used by other vendor's instruments for clock synchronization. Such AWGs are widely deployed in today's optical test laboratories (like e.g. the Keysight<sup>®</sup> M8196A).

With such a connection of instruments is it possible to enhance the speed and the capabilities of different vendors AWGs<sup>1</sup> with one of SHF's remote head modules. This makes it possible e.g. to generate 120 GBaud PAM4 signals with Keysight's<sup>®</sup> M8196 A connected to SHF's 616 C PAM-Multiplexer.

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 2/18

<sup>&</sup>lt;sup>®</sup> Keysight is a registered trademark of Keysight Technologie Inc.

<sup>&</sup>lt;sup>1</sup> With SHF's BPGs or AWGs a clock distribution is not required as our instruments provide all required clock signals right away.

# **Block Diagram**

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 3/18

# Accessories

- +12 V Power Supply Desktop Adapter

- Functional Earth Cable

- Mini-USB cable

# **Absolute Maximum Ratings**

| Parameter                                 | Unit | Symbol              | Min. | Тур. | Max. | Comment          |

|-------------------------------------------|------|---------------------|------|------|------|------------------|

| Input Parameters                          |      |                     |      |      |      |                  |

| Input Amplitude                           | mV   | V <sub>Clk</sub> in |      |      | 1000 | Peak-to-Peak     |

| External DC Voltage on<br>RF Input Port   | V    | $V_{\text{DC}}$ in  | -6   |      | +6   | AC coupled port  |

| External DC Voltage on<br>RF Output Ports | V    | VDC out             | -6   |      | +6   | AC coupled ports |

| DC Supply Voltage                         | V    | Vcc                 | 0    |      | +14  |                  |

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 4/18

# Specifications – SHF C991 A

| Parameter                  | Unit             | Symbol           | Min.     | Тур. | Max. | Comment                                                          |  |

|----------------------------|------------------|------------------|----------|------|------|------------------------------------------------------------------|--|

| Input Frequency            |                  |                  |          |      |      |                                                                  |  |

| Minimum Input Frequency    | GHz              | fin min          |          |      | 4    | N₁ ≤ 20                                                          |  |

| Maximum Input Frequency    | GHz              | fin max          | 48<br>64 |      |      | N <sub>1</sub> = 1<br>N <sub>1</sub> ≥ 2                         |  |

| Input Amplitude            |                  |                  |          |      |      |                                                                  |  |

| Input Amplitude            | mV <sub>pp</sub> | Vin              | 200      | 600  | 900  | AC coupled<br>Single ended                                       |  |

| Output Frequency           |                  |                  |          |      |      |                                                                  |  |

| Clock Out                  | GHz              | f <sub>out</sub> | 4        |      | 64   | fin                                                              |  |

| Clock /2 Out               | GHz              | f <sub>out</sub> | 2        |      | 32   | f <sub>in</sub> /2                                               |  |

| Clock DIV <sub>1</sub> Out | GHz              | f <sub>out</sub> | 0.10     |      | 24   | f <sub>in</sub> /(2×N <sub>1</sub> )<br>N <sub>1</sub> = 1…127   |  |

| Clock DIV <sub>2</sub> Out | GHz              | fout             | 0.05     |      | 3    | $f_{in} / (2 \times N_1 \times N_2)$<br>N <sub>2</sub> = 1,2,4,8 |  |

| Output Amplitude           |                  |                  |          |      |      |                                                                  |  |

| Clock Out                  | $mV_{pp}$        | V <sub>out</sub> | 300      |      | 700  | AC coupled<br>Single ended                                       |  |

| Clock /2 Out               | mV <sub>pp</sub> | Vout             | 600      |      | 900  | AC coupled<br>Single ended                                       |  |

| Clock DIV1 Out             | mV <sub>pp</sub> | Vout             | 500      |      | 900  | AC coupled<br>Single ended                                       |  |

| Clock DIV <sub>2</sub> Out | mV <sub>pp</sub> | Vout             | 600      |      | 900  | AC coupled<br>Single ended                                       |  |

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 5/18

# Specifications – SHF C991 A

| Parameter                           | Unit | Symbol               | Min.  | Тур.         | Max.  | Comment                                                          |  |

|-------------------------------------|------|----------------------|-------|--------------|-------|------------------------------------------------------------------|--|

| Power Requirement                   |      |                      |       |              |       |                                                                  |  |

| Supply Voltage                      | V    | Vcc                  | +11.5 | +12.0        | +12.5 |                                                                  |  |

| Supply Current                      | A    | Icc                  |       | 0.69<br>0.95 |       | Without heat sink<br>With heat sink                              |  |

| Power Dissipation                   | W    | Pd                   |       | 8.3<br>11.4  |       | Without heat sink<br>With heat sink<br>@ V <sub>CC</sub> = +12 V |  |

| Integrated Fan Control <sup>2</sup> |      |                      |       |              |       |                                                                  |  |

| Output Voltage Fan                  | V    | V <sub>Fan+12V</sub> |       | +12          |       |                                                                  |  |

| Output Current Fan                  | А    | I <sub>Fan+12V</sub> |       | 0.26         |       |                                                                  |  |

| Output Frequency Fan                | Hz   | f <sub>Fan+12V</sub> |       | 30           |       |                                                                  |  |

| Input Tacho Fan                     | V    | VFan Tacho           |       | 3.3          |       |                                                                  |  |

| Mechanical Characteristics          |      |                      |       |              |       |                                                                  |  |

| Clock In                            | Ω    |                      |       | 50           |       | 1.85 mm (V) female                                               |  |

| Clock Out                           | Ω    |                      |       | 50           |       | 1.85 mm (V) female                                               |  |

| Clock /2 Out                        | Ω    |                      |       | 50           |       | 2.92 mm (K) female                                               |  |

| Clock DIV1 Out                      | Ω    |                      |       | 50           |       | 2.92 mm (K) female                                               |  |

| Clock DIV <sub>2</sub> Out          | Ω    |                      |       | 50           |       | 2.92 mm (K) female                                               |  |

| Dimensions                          | mm   |                      |       |              |       | See Outline Drawing pages 17 / 18                                |  |

| Weight                              | g    |                      |       | 190<br>480   |       | Without heat sink<br>With heat sink                              |  |

| Conditions                          |      |                      |       |              |       |                                                                  |  |

| Operating Temperature               | °C   | Tambient             | 15    |              | 35    |                                                                  |  |

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 6/18

<sup>&</sup>lt;sup>2</sup> Use only with the supplied heat sink and fan!

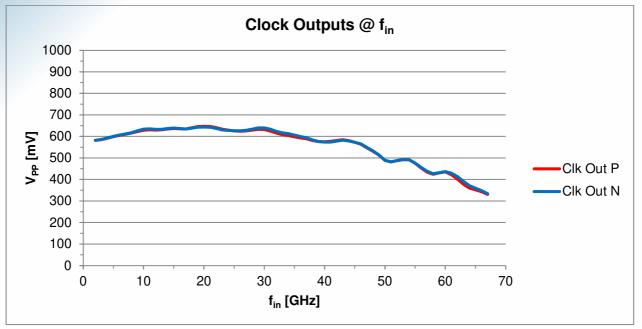

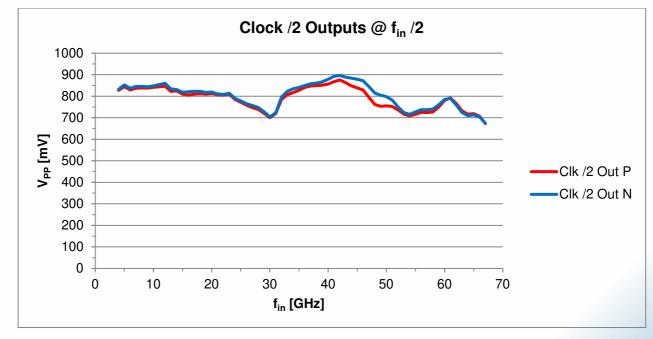

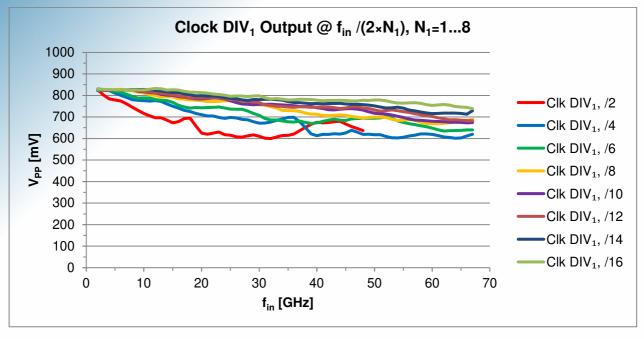

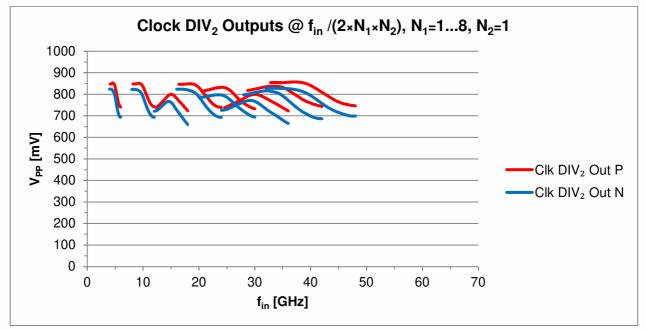

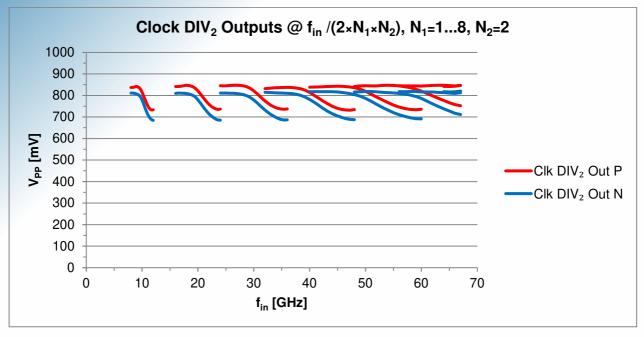

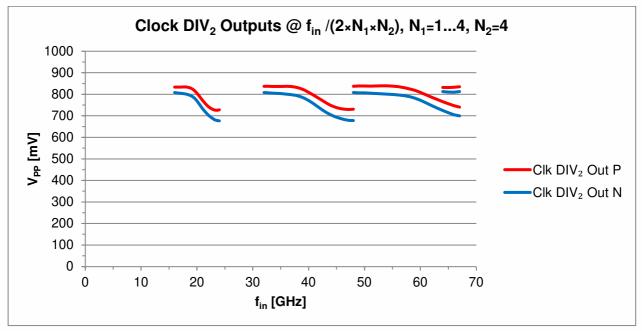

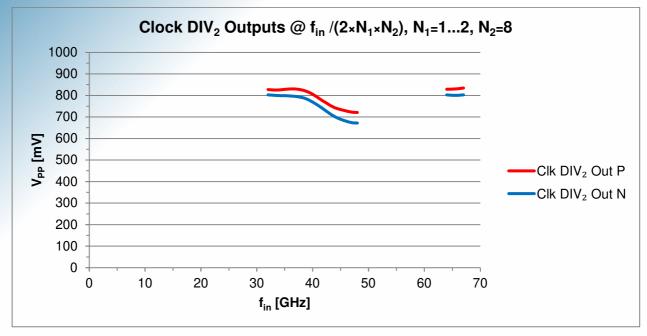

# **Typical Output Amplitudes** @ 2.0 GHz $\leq$ Clk DIV<sub>2</sub> $\leq$ 3.0 GHz

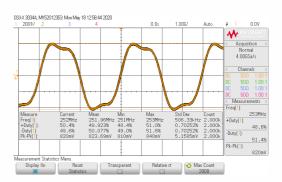

The measurements below have been performed using an Anritsu<sup>®</sup> signal generator (MG3697C) and a Tektronix<sup>®</sup> Digital Serial Analyzer (DSA8300) with a Phase Reference Module (82A04B-60G) and a 70 GHz Sampling Module (80E11). The outputs of the Clock distribution module had been connected directly to the DSA input. Input power of the clock signal is 0 dBm (630 mV<sub>pp</sub>).

**Clock /2 Outputs**

<sup>®</sup> Anritsu is a registered trademark of Anritsu Corporation, Tektronix is a registered trademark of Tektronix Inc.

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 7/18

Clock DIV<sub>1</sub> Output, N<sub>1</sub>=1...8

### Clock DIV<sub>2</sub> Outputs, N<sub>2=1</sub>

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 8/18

### Clock DIV<sub>2</sub> Outputs, N<sub>2=4</sub>

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 9/18

Clock DIV<sub>2</sub> Outputs, N<sub>2=8</sub>

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 10/18

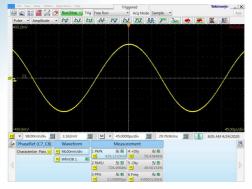

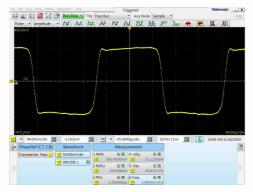

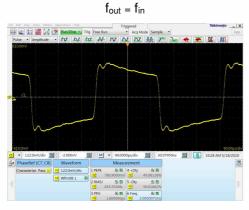

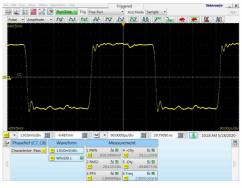

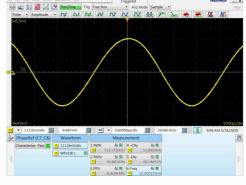

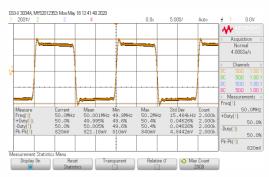

# **Typical Output Waveforms** @ 2.0 GHz $\leq$ Clk DIV<sub>2</sub> $\leq$ 3.0 GHz

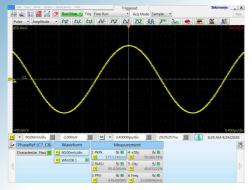

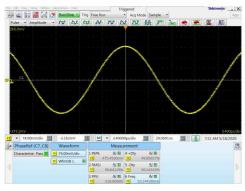

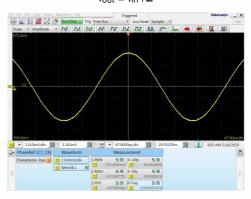

The measurements below have been performed using an Anritsu<sup>®</sup> signal generator (MG3697C) and a Tektronix<sup>®</sup> Digital Serial Analyzer (DSA8300) with a Phase Reference Module (82A04B-60G) and a 70 GHz Sampling Module (80E11). The outputs of the Clock distribution module had been connected directly to the DSA input. Input power of the clock signal is 0 dBm (630 mV<sub>pp</sub>).

#### Clock Outputs @ 4.0 GHz Clock Input

4.0 GHz input signal

4.0 GHz output signal @ Clk Out

2.00 GHz output signal @ Clk DIV1 Out  $f_{out} = f_{in} \ /(2 \times N1), \ N1 = 1$

2.0 GHz output signal @ Clk /2 Out  $f_{out} = f_{in} /2$

2.00 GHz output signal @ Clk DIV<sub>2</sub> Out  $f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 1, N_2 = 1$

<sup>®</sup> Anritsu is a registered trademark of Anritsu Corporation, Tektronix is a registered trademark of Tektronix Inc.

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 11/18

### Clock Outputs @ 53.0 GHz Clock Input

53.0 GHz input signal

53.0 GHz output signal @ Clk Out

5.30 GHz output signal @ Clk DIV1 Out  $f_{out} = f_{in} \ /(2{\times}N1), \ N1{=}5$

26.5 GHz output signal @ Clk /2 Out  $f_{out} = f_{in} \ /2$

2.65 GHz output signal @ Clk DIV<sub>2</sub> Out  $f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 5, N_2 = 2$

### Clock Outputs @ 64.0 GHz Clock Input

64.0 GHz input signal

64.0 GHz output signal @ Clk Out

5.33 GHz output signal @ Clk DIV1 Out  $f_{out} = f_{in} \ /(2{\times}N1), \ N1{=}6$

32.0 GHz output signal @ Clk /2 Out  $f_{out} = f_{in} \ /2$

2.67 GHz output signal @ Clk DIV<sub>2</sub> Out  $f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 6, N_2 = 2$

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 13/18

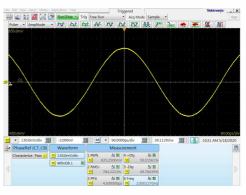

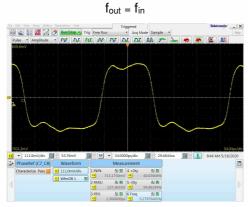

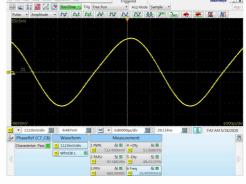

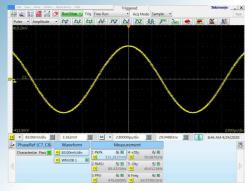

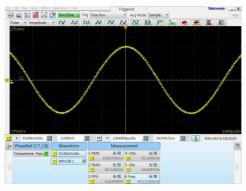

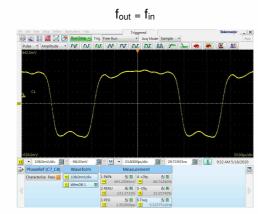

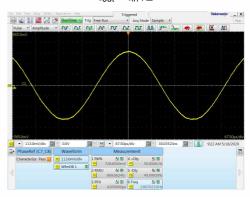

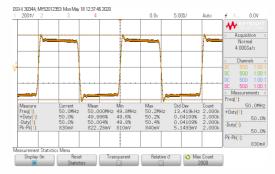

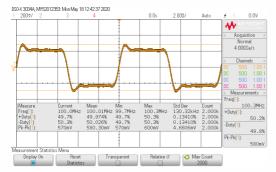

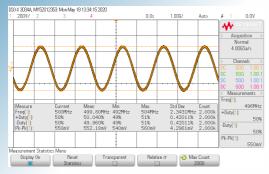

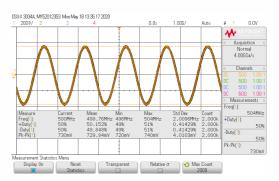

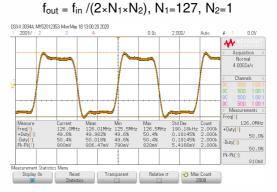

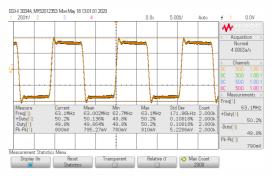

# **Typical Output Waveforms @ Clk DIV<sub>2</sub> < 2.0 GHz**

The measurements below have been performed using an Anritsu<sup>®</sup> signal generator (MG3697C) and a Keysight<sup>®</sup> Digital Storage Oscilloscope (DSO-X 3034A). The outputs of the Clock distribution module had been connected directly to the DSO input. Input power of the clock signal is 0 dBm (630 mV<sub>pp</sub>).

#### Clock Outputs @ 4.0 GHz Clock Input, N1=20

50 MHz output signal @ Clk DIV<sub>2</sub> Out

$f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 20, N_2 = 2$

### 50 MHz output signal @ Clk DIV<sub>2</sub> Out $f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1=32, N_2=2$

#### Clock Outputs @ 6.4 GHz Clock Input, N1=32

100 MHz output signal @ Clk DIV1 Out

$f_{out} = f_{in} / (2 \times N_1), N_1 = 32$

<sup>®</sup> Anritsu is a registered trademark of Anritsu Corporation, Keysight is a registered trademark of Keysight Technologie Inc.

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 14/18

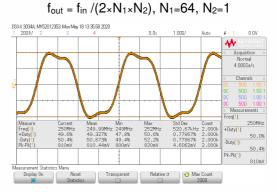

#### Clock Outputs @ 64.0 GHz Clock Input, N1=64

500 MHz output signal @ Clk DIV1 Out

$f_{out} = f_{in} / (2 \times N_1), N_1 = 64$

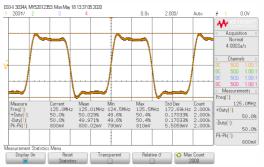

#### 500 MHz output signal @ Clk DIV<sub>2</sub> Out

#### 250 MHz output signal @ Clk DIV<sub>2</sub> Out

$f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 64, N_2 = 2$

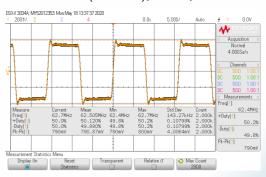

#### 2.67 MHz output signal @ Clk DIV<sub>2</sub> Out

#### $f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 64, N_2 = 4$

#### 62.5 MHz output signal @ Clk DIV<sub>2</sub> Out

$f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 64, N_2 = 8$

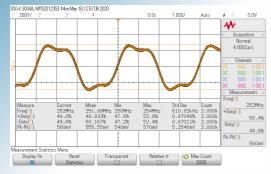

#### Clock Outputs @ 64.0 GHz Clock Input, N1=127

251.97 MHz output signal @ Clk DIV1 Out

$f_{out} = f_{in} / (2 \times N_1), N_1 = 127$

#### 251.97 MHz output signal @ Clk DIV<sub>2</sub> Out

#### 125.98 MHz output signal @ Clk DIV<sub>2</sub> Out

$f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 127, N_2 = 2$

62.99 MHz output signal @ Clk DIV<sub>2</sub> Out

$f_{out} = f_{in} / (2 \times N_1 \times N_2), N_1 = 127, N_2 = 4$

A

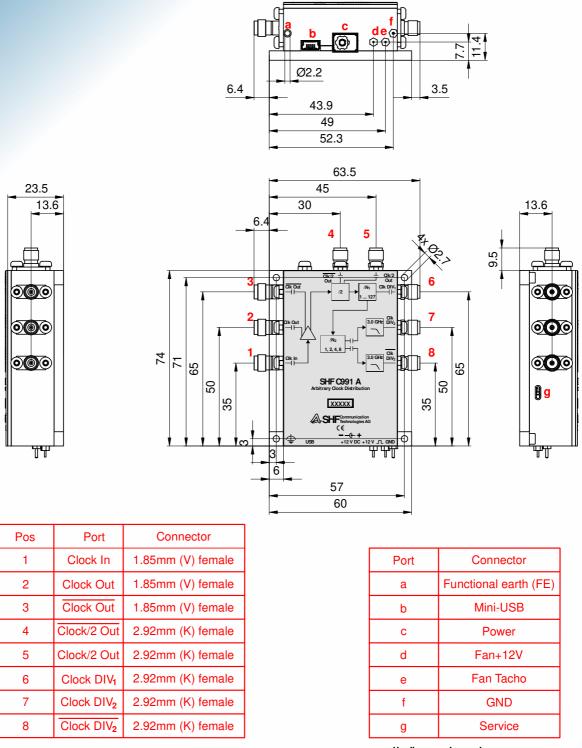

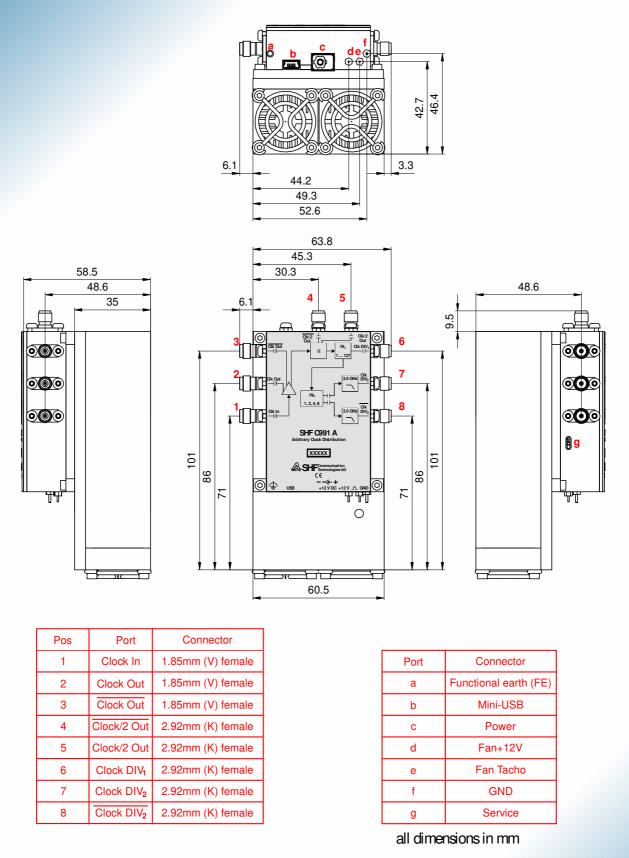

# **Mechanical Drawing**

all dimensions in mm

SHF reserves the right to change specifications and design without notice – SHF C991 A - V001 June 12, 2020 Page 17/18

A

# **Mechanical Drawing**

SHF reserves the right to change specifications and design without notice - SHF C991 A - V001 June 12, 2020 Page 18/18